次世代ホログラフィックイメージング向けの高性能並列演算

High-performance parallel computing for next-generation holographic imaging

2018年4月17日 Nature Electronics 1 : 254 doi: 10.1038/s41928-018-0057-5

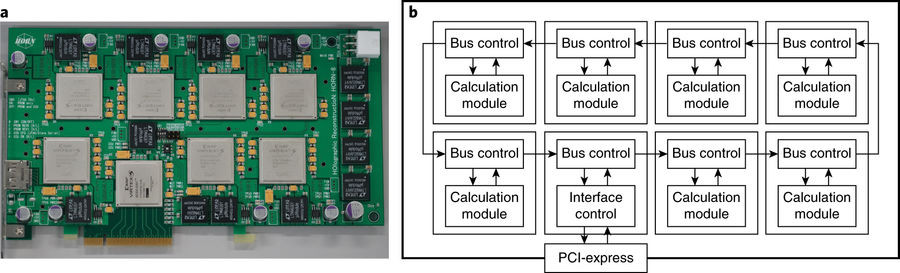

ホログラフィは三次元(3D)画像を記録し再生する方法である。コンピュータの普及により、ホログラフィを用いた3D映像システム(エレクトロホログラフィ)の開発が進められるようになったが、実用化には至っていない。理由は、ホログラムには膨大な量のデータが必要であり、現状の計算パワーではこれだけ大量のデータを実時間で処理することができないからである。我々は今回、8個の大規模フィールド・プログラマブル・ゲートアレイを用いたホログラフィ専用計算ボードを開発して、ビデオフレームレートで更新できる10 8ピクセルのホログラムを生成した。我々のシステムでは、4,480のホログラム計算回路を単一ボード上で並列動作させることができ、このボードを8枚クラスター化して並列計算数を35,840まで増やすことができる。我々は、7,877 点からなる3D画像を使用して、108ピクセルのホログラムをビデオレートで更新することができ、3Dムービーを投影できることを示す。並列回路の数を増やすと、これに比例してシステムの速度が増加することも実証する。システムは0.25 GHzで動作するが、これは0.5 ペタフロップス(1ペタフロップスは毎秒1015回の浮動小数点演算が可能)に相当する速度であり、高性能コンピュータに匹敵する。

Corresponding Author

Holography is a method of recording and reproducing three-dimensional (3D) images, and the widespread availability of computers has encouraged the development of holographic 3D screens (electroholography). However, the technology has not yet been used in practical applications because a hologram requires an enormous volume of data and modern computing power is inadequate to process this volume of data in real time. Here, we show that a special-purpose holography computing board, which uses eight large-scale field-programmable gate arrays, can be used to generate 108-pixel holograms that can be updated at a video frame rate. With our approach, we achieve a parallel operation of 4,480 hologram calculation circuits on a single board, and by clustering eight of these boards, we can increase the number of parallel calculations to 35,840. Using a 3D image composed of 7,877 points, we show that 108-pixel holograms can be updated at a video rate, thus allowing 3D movies to be projected. We also demonstrate that the system speed scales up in a linear manner as the number of parallel circuits is increased. The system operates at 0.25 GHz with an effective speed equivalent to 0.5 petaflops (1015 floating-point operations per second), matching that of a high-performance computer.